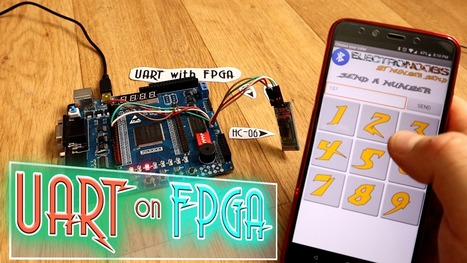

This are some small examples on the UART communication on FPGAs. The codes are very easy. First we see the RX code so how to receive data, then the TX code and finally we will make a TOP.v code and merge everything together. My FPGA has a 50MHz clock. My UART communication will work at 9600 bauds. For taht we need to make another module called baud rate generator and create some "tick" pulses 16 time faster than 9600 bauds, and with that syncronize the data read/write exactly in the middle of the bit.

Research and publish the best content.

Get Started for FREE

Sign up with Facebook Sign up with X

I don't have a Facebook or a X account

Already have an account: Login

Your new post is loading... Your new post is loading...

Your new post is loading... Your new post is loading...

|